触发器

触发器种类很多。按照时钟控制信号来分,有电位触发、边沿触发和主-从触发等方式。对使用者来说,在选用触发器时,若触发方式不当,系统不能达到预期设计要求。

电位触发方式触发器(电位触发器)

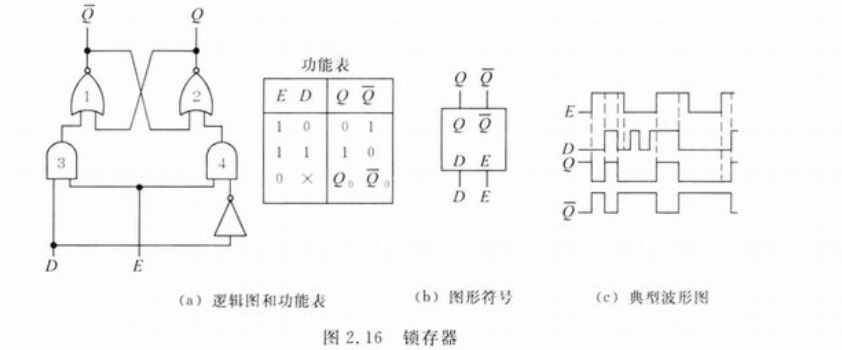

电位触发器结构简单,在计算机中常用来组成暂存器。

图 2.16 给出了被称为锁定触发器(又称锁存器)的电位触发器的逻辑图、功能表和波形图。当 E 为 1 时,D 和 ~D 进入(由门1 和门2 组成的)基本触发器,此时Q = D, ~Q = ~D; 当 E为 0 时,D 和 ~D 被锁存,触发器状态保持不变,而且以E 从 “1” 转变到 “0” 时的电平来决定E = 0 期间Q 的状态。

边沿触发方式触发器(D触发器)

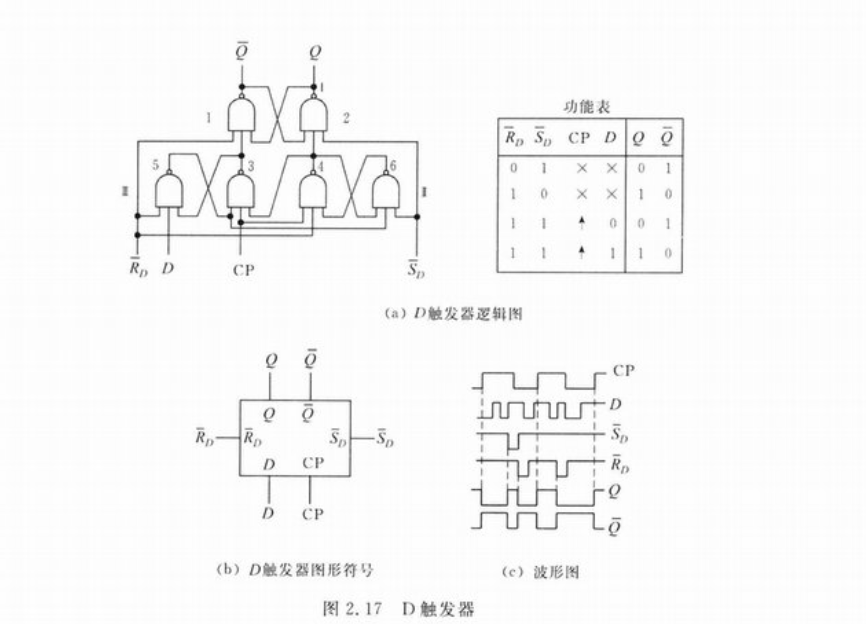

触发器接受的是时钟脉冲CP某一约定跳变(正跳变和负跳变)来到时的输入数据。在CP = 1 及 CP = 0期间以及CP非约定跳变到来时,触发器不接收数据。

常用的正边沿触发器是D触发器,图2.17是它的逻辑图和典型波形图。门1 和 门2构成基本触发器;~RD和~SD分别将触发器清零和置一;门3~门6起维持阻塞作用,保证把CP正确并完整地送到基本触发器。

在计算机硬件电路设计中,为了提高运行的稳定性,很重视维持阻塞技术的使用。

D触发器在CP正跳变以外期间出现在D端的数据变化和干扰不会被接收,因此,具有很强的抗干扰的能力而被广泛应用,可用来组成寄存器、计数器和移位寄存器等。

主-从触发方式触发器(J-K触发器)

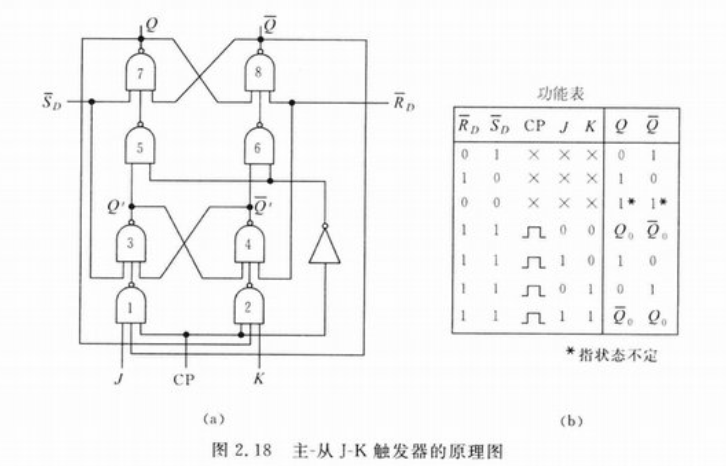

主从触发器基本上是由两个电位触发器级联而成的,接收输入数据的是主触发器,接收主触发器输出的是从触发器,主、从触发器的同步控制信号是互补的(CP和~CP)。

图2.18(a)是主-从J-K触发器的原理图,触发器的输出Q、~Q分别和接收K、J数据的输入门相连。在CP = 1 期间主触发器接收数据;在CP负跳变来到时,从触发器接收主触发器最终的状态。图2.18(b)是主-从J-K触发器功能表。

主从触发器由于具有计数功能,常用于组成计数器。

寄存器和移位寄存器

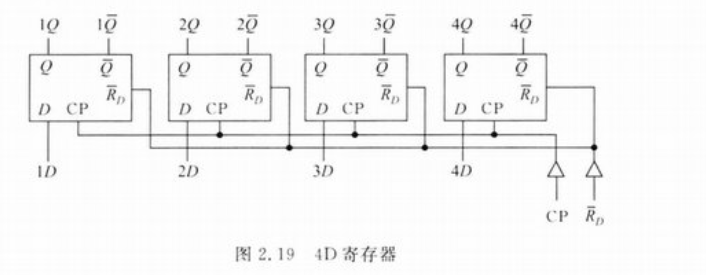

寄存器是用于暂存数据和指令的计算机中的重要部件。它由触发器和一些控制门组成。常见的寄存器有D触发器和锁存器。

图2.19所示是由正沿触发的D触发器组成的4位寄存器。在CP正沿作用下,外部数据才能进入寄存器。

在计算机中常要求寄存器由移位功能。例如在进行乘法时,要求将部分积右移;在将并行器转换成串行行数时也需移位。有移位功能的寄存器称为移位寄存器。此时应增加逻辑电路来触发器的输入数据(1D~4D)。

计数器

计数器是计算机和数字仪表中常用的一种电路。计数器中各触发器的时钟信号由同一脉冲提供的称为同步计数器,各触发器是同时翻转的。

这种同步性使得计数器的操作更加精确和可靠,避免了由于不同触发器之间的时钟偏差而导致的错误计数。

同步计数器的主要特点是,当输入信号变化时,只有在时钟信号的上升沿或下降沿到来时,触发器才会根据输入信号进行状态转换,从而更新计数值。由于所有触发器都受到相同时钟信号的控制,它们的操作是同步的,这就确保了计数值的准确性。

在数字电路和系统设计中有着广泛的应用,特别是在需要精确计数的场合,如频率测量、事件计数等。通过合理设计同步计数器的结构和参数,可以实现各种复杂的计数功能,满足不同的应用需求。

阵列逻辑电路

“阵列”是指逻辑元件在硅芯片上以阵列形式排列,电路具有用户自编程以及减少系统的硬件规模等优点。

下面简单介绍以下阵列逻辑电路:

只读存储器(ROM)

只读存储器(ROM)用于存储固定的信息(如监控程序、函数和常数等)。在使用前把信息存入其中,使用时读出已存入的信息,而不能写入新的信息。

ROM主要是由全译码的地址译码器和存储单元体组成,前者是一种“与”阵列,后者是一种“或”阵列。

存储体中写入的信息是由用户事先决定的,称为用户“可编程”的,而地址译码器则是用户“不可编程”的

可编程序逻辑阵列(PLA)

可编程序逻辑阵列由与阵列、或阵列组成,两者都是用户可编程的。PLA在组成控制器、存储固定函数以及实现随机逻辑中有广泛的应用。

可编程序阵列逻辑(PAL)

可编程序阵列逻辑(PAL)的与阵列是用户可编程的,而或阵列是用户不可编程的。PAL也有广泛的应用。

通用阵列逻辑(GAL)

通用阵列逻辑比PAL功能更强。在它的输出有一个逻辑宏单元,通过对它的编程,可以获得多种输出形式,从而使功能大大增强。

门阵列(GA)

门阵列是一种逻辑功能很强的阵列逻辑电路。在芯片上制作了排成阵列形式的门电路,根据用户需要对门阵列中的门电路进行互连设计,再通过集成电路制作工艺来实现互连,以实现所需的逻辑功能。

宏单元阵列(MCA)

宏单元阵列是一种比GA功能更强、集成度更高的阵列电路,在芯片上排列成阵列的除门电路外,还有触发器、加法器、寄存器以及ALU等。

现场可编程门阵列(FPGA)

现场可编程门阵列是一种集编程设计灵活性和宏单元阵列于一体的高密度电路。它与GA和MAC有区别,FPGA内部按阵列分布的 宏单元块都是用户可编程的。用户所需逻辑在软件支持下,由用户自己接入来实现,而无须集成电路制造工厂介入,并且这种装入是可以修改的,因而其连接极为灵活。

上述阵列逻辑电路统称为可编程序逻辑器件(PLD)。